HiDFT-STAR |

|

|

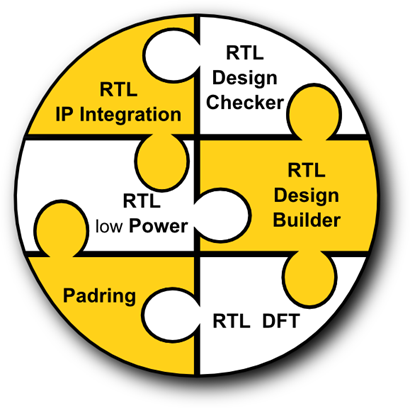

Traditionally, designers have used various insertion methods for RTL logic, by combining either manual or semi automated RTL insertion with post synthesis gate level insertion. Design verification is directly impacted by such a process: late design verification, error prone when designers intervene manually on gate-level netlists, break or modify timing paths, etc. Inserting automatically different structures (ports, connections, memories & glue logic) fully at RTL avoids such problems, and most importantly helps in verifying complex IP cores and SoCs early in the design flow. In conjunction with automated RTL insertion tools, extendible and simulation-free design verification tools working at RTL (checking port connections like for memories, clock gating logic, pin Muxing, clock trees, etc.) are required. STAR is a fully customizable Tcl-based RTL-to-RTL editing and verification platform. It supports both RTL and gate-level. STAR can be considered as an add-on toolbox to current design and verification EDA flows where several editing and verification tools working at both RTL and gate are provided: STAR-CK : Structural clock tree verification at RTL STAR-Power : RTL structural power verification and automatic insertion of low power structures STAR-Build : Automatic block merge and RTL generation STAR-ECO : Gate-level and RTL Engineering Change Order with automated generation of gate and RTL STAR-Debug : RTL and gate-level design exploration, pin to pin tracing and debug of complex IP cores and SoCs |

|

|

|

|

The above tools can be considered in the same session, with the ability for a user to move from one tool to another. For example, edit a new RTL, check internal clocks within the block then run power DRC, and make RTL fixes effortlessly all in the same session. Leading semiconductor companies are finding in STAR the best platform in the market to get rid of difficult to maintain internal Perl/Tcl scripts with unique extension capabilities. With STAR, a designer has no longer needs to write or maintain Perl or Tcl scripts for custom RTL + gate editing. He/she has direct access to built-in editing and verification mechanisms with powerful and unique extension capabilities. Also, a user can build a regression type environment and use it in a press button mode in case of any design change. |

|